#### **ARTICLE**

# Latest VLSI Techniques for 3nm Technology for Building Efficient AI Chips

Q. Zhang,\* H. Deng, and K. Song

Department of Electronics Engineering, Chang Gung University, Taoyuan 333, Taiwan

\*Corresponding author: zhangq65@mail.cgu.edu.tw

(Received: 17 February 2024; Revised: 29 July 2024; Accepted: 21 August 2024; Published: 02 September 2024)

#### **Abstract**

Modern AI chip design has achieved a remarkable milestone, delivering 10X productivity gains through advanced automation and machine learning optimization. Specifically, these improvements allow engineers to create more efficient designs while significantly reducing time-to-market. The integration of artificial intelligence into VLSI chip design has revolutionized how we approach complex semiconductor development. In fact, these technologies now enable the integration of billions of transistors onto a single chip, while optimizing power, performance, and area (PPA) for maximum efficiency. Furthermore, AI-driven predictive modeling helps identify potential issues early in the design phase, ensuring better outcomes before physical implementation. We will explore the latest techniques in 3nm technology, covering everything from process node fundamentals to thermal management systems. Our comprehensive guide examines power management architectures, memory integration methods, and neural processing unit designs that are essential for creating high-performance AI chips in today's competitive landscape.

Keywords: 3nm Technology; AI Chips; Energy Efficiency; Low Power Design; VLSI Techniques; Semiconductor Technology

**Abbreviations:** ATE: Automated test equipment, CPP: Contacted poly pitch, DVFS: Dynamic Voltage and Frequency Scaling, EUV: Extreme ultraviolet, GAA: Gate-All-Around

## 1. 3nm Process Node Fundamentals

The semiconductor industry has reached a critical milestone with the 3nm process node, marking a significant advancement in chip manufacturing capabilities. The 3nm node represents precise specifications, including a gate length of 16-18nm and a metal pitch of 30nm [1, 2, 3, 4].

# 1.1 Gate Length Scaling Challenges at 3nm

At the 3nm process node, traditional transistor scaling faces unprecedented physical limitations. When fin width reaches 5nm, the contacted poly pitch (CPP) hits a threshold of approximately 45nm. Additionally, quantum effects begin to dominate at these dimensions, leading to substantial power leakage concerns as given in Table 1 [5, 6, 7]:

# 1.2 Advanced Lithography Requirements

Extreme ultraviolet (EUV) lithography emerges as a cornerstone technology for 3nm chip production. The EUV system operates at a wavelength of 13.5nm, enabling the printing of intricate features. Nevertheless, EUV faces new hurdles at 3nm that necessitate multipatterning techniques [8, 9, 10].

<sup>© 2024</sup> by the authors. Licensee FMR, Netherlands. This is an Open Access article, distributed under the terms of the Creative Commons Attribution 4.0 International (CC BY 4.0) licence (https://creativecommons.org/licenses/by/4.0/)

| Parameter   | 5nm Node | 3nm Node |

|-------------|----------|----------|

| Gate Length | 18-20nm  | 16-18nm  |

| Gate Pitch  | 48nm     | 45nm     |

| Metal Pitch | 32nm     | 30nm     |

Table 1. Gate Length Scaling Challenges at 3nm

The industry has developed innovative solutions through high-NA EUV systems as given in Table 2:

| Feature    | Specification | Benefit             |

|------------|---------------|---------------------|

| NA Value   | 0.55          | Higher contrast     |

| Resolution | 8nm           | Better precision    |

| Throughput | 185 wph       | Improved efficiency |

Table 2. Advanced Lithography Requirements

# 1.3 Material Innovation for 3nm Chips

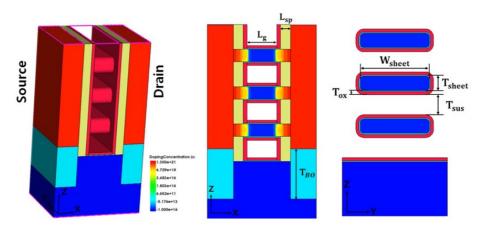

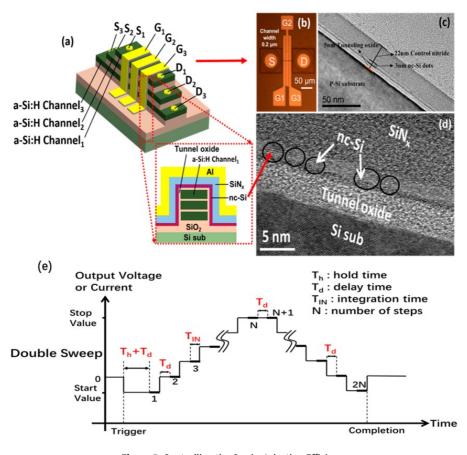

Material selection plays a crucial role in overcoming the limitations of silicon-based processes. The industry explores alternative materials including: The manufacturing process requires extreme precision in material deposition. For instance, the formation of nanosheet FETs demands careful control during the epitaxial deposition of alternating silicon-germanium and silicon layers. Moreover, the development of dry resist technology presents promising alternatives to traditional wet resists, offering improved resolution and reduced effectivity as in Fig. 1 [11, 12, 13, 14].

Figure 1. Cross-sectional views of FinFET

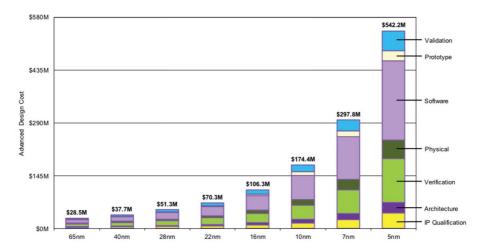

The cost implications of these advancements are substantial, with 3nm chip design costs reaching approximately USD 590 million, compared to USD 416 million for 5nm designs. Nevertheless, the benefits include enhanced performance metrics, with TSMC's N3E process technology demonstrating 1.6× higher logic transistor density and 10-15% improved performance at iso power.

The industry continues to address reliability challenges at 3nm. Mechanical stresses after die thinning, package integration considerations, and the monitoring of potential latent defects require so-

phisticated solutions. Furthermore, the increasing importance of inductance effects at lower metallization levels demands careful attention to exotic metal selection and implementation.

The transition to 3nm technology brings forth quantum mechanical considerations that were previously negligible. These effects now require probabilistic modeling and enhanced control mechanisms to ensure reliable circuit operation. Additionally, the alignment precision at these dimensions becomes critical, as even minor misplacements can significantly impact chip functionality and yield [15, 16, 17, 18].

# 2. Power Management Architecture

Power management emerges as a critical factor in 3nm AI chip design, particularly as environmental sustainability drives innovation in semiconductor manufacturing. The emphasis on delivering energy-efficient compute extends across various computing platforms, from AI servers to everyday devices like smartphones and laptops [19, 20, 21].

# 2.1 Dynamic Voltage Frequency Scaling at 3nm

Dynamic Voltage and Frequency Scaling (DVFS) stands as an essential technique for managing power consumption in modern computing systems. The implementation requires careful consideration of voltage-frequency pairs, as shown in the following table as given in Table 3 [22, 23]:

| Operating Mode | Frequency    | Voltage | Power Savings |

|----------------|--------------|---------|---------------|

| Active Mode    | 125MHz       | 1.08V   | Baseline      |

| Slow Mode      | 66MHz        | 0.9V    | 40-70%        |

| Standby Mode   | Powered Down | 0V      | Maximum       |

Table 3. Dynamic Voltage Frequency Scaling at 3nm

The 3nm process demonstrates remarkable improvements in power efficiency. TSMC's N3E process achieves 34% power reduction, whereas Samsung's 3nm process reduces power consumption by up to 45%. Subsequently, the implementation of DVFS at 3nm requires sophisticated PVT (Process, Voltage, Temperature) sensors operating at 100KS/s sampling rates to ensure rapid detection of environmental changes [24, 25, 26].

## 2.2 Leakage Current Control Methods

At the 3nm node, controlling leakage current becomes increasingly challenging due to quantum effects. The following table illustrates the relationship between different process variants and their leakage characteristics as given in Table 4:

| Process Variant | Performance Gain | Power Leakage |

|-----------------|------------------|---------------|

| N3E Baseline    | 18%              | Standard      |

| N3P             | 5%               | 5-10% reduced |

| N3X             | 5% higher clocks | 250% increase |

Table 4. Leakage Current Control Methods

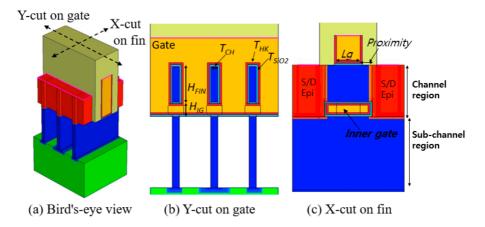

The Gate-All-Around (GAA) architecture represents a significant advancement in leakage control. This design completely surrounds the channel with the gate on all four sides, offering superior electron control. The implementation of GAA at 3nm has shown remarkable results, with Samsung's

second-generation technology demonstrating 3.4 times improvement in single-core performance [27, 28, 29].

Process variations play a crucial role in leakage management. The PVT sensor technology supports process corner detection for TT (Typical-Typical), FF (Fast-Fast), and SS (Slow-Slow) variations, enabling precise calibration of power delivery systems. The voltage monitoring range extends from 0.3V to 1.0V, with a resolution of 0.3mV, ensuring fine-grained control over power consumption as in Fig. 2.

Figure 2. FinFET-based vertical GAA-FinFET

The implementation of these power management techniques requires careful consideration of the process window and yields. N3E utilizes up to 19 EUV layers without relying on EUV double patterning, thereby reducing complexity and costs. The threshold voltage (Vth) control becomes particularly critical, as it directly influences the gate's ability to manage current flow. The interface flatness of the gate/dielectric layer/channel stacking structure plays a vital role in controlling the work function difference [30].

The integration of these power management techniques allows AI chips to operate efficiently across various workload conditions. The materials engineering solutions improve surface properties for void-free copper reflow, reducing electrical line resistance by up to 25%. This advancement, coupled with sophisticated power management architectures, ensures optimal performance while maintaining power efficiency at the 3nm node [31, 32].

# 3. Memory Integration Techniques

Memory integration at 3nm presents unique challenges, as SRAM scaling faces unprecedented limitations in density improvements. Recent findings reveal that SRAM did not achieve significant shrinkage at 3nm, maintaining almost identical bitcell dimensions to the 5nm node [33].

## 3.1 High-Density Cache Design

The density constraints at 3nm necessitate innovative approaches to cache design. TSMC's N3E process demonstrates only a 4% boost in transistor density for mixed chip designs comprising 50% logic, 30% SRAM, and 20% analog circuits. The following table illustrates the SRAM density comparison across nodes as given in Table 5:

Table 5. High-Density Cache Design

| Node | SRAM Density Improvement | Bitcell Characteristics |

|------|--------------------------|-------------------------|

| N3B  | 5% over N5               | Standard Configuration  |

| N3E  | No improvement           | Identical to N5         |

| N5   | Baseline                 | Reference Design        |

# 3.2 Memory Controller Optimization

Memory controller design at 3nm focuses on managing multiple memory types efficiently. The hierarchy typically incorporates as given in Table 6:

Table 6. Memory Controller Optimization

| Memory Type  | Bandwidth          | Power Efficiency | Capacity       |

|--------------|--------------------|------------------|----------------|

| On-chip SRAM | Tens of TB/s       | Highest          | Few hundred MB |

| НВМ          | 1024 wires @ 2Gbps | Very Good        | 8GB+           |

| GDDR6        | 32 wires @ 16Gbps  | Good             | Multiple GB    |

The implementation of high-bandwidth memory (HBM) introduces sophisticated stacking techniques, utilizing silicon interposers for connecting 1,024 data wires operating at two gigabits per second. Alternatively, GDDR6 memory systems employ 32 data wires running at substantially higher speeds of up to 16Gbps, offering a practical balance between performance and implementation complexity [34].

## 3.3 Power-Aware Memory Subsystems

Power-aware memory design emerges as a critical factor in 3nm AI chips. The implementation of power-aware memory balancing determines optimal configurations through sophisticated algorithms that consider the number of memory blocks, decoder circuits, and multiplexer arrangements.

Advanced memory solutions like LPCAMM2 demonstrate remarkable power efficiency improvements. Compared to traditional DDR5, LPCAMM2 achieves up to 85% lower power consumption in active cases. This efficiency becomes particularly crucial as NPUs and iGPUs share system memory within unified memory architectures.

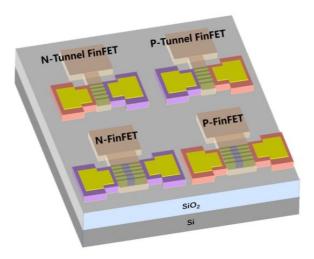

The reliability aspects of memory integration at 3nm demand careful consideration of various physical effects. Engineers must account for mechanical stresses after die thinning, particularly when integrating memory into advanced packages or interposers. Additionally, the increasing prominence of analog-like behavior in digital circuits necessitates attention to electromagnetic interference and signal drift as in Fig. 3 [35].

Memory testing at 3nm introduces new complexities, especially regarding latent defects and test coverage gaps. Traditional testing methods that primarily focused on sort/yield and final package testing now require supplementation with advanced inspection techniques. Machine learning algorithms assist in analyzing sophisticated image data to determine manufacturing quality and potential reliability issues [36].

The integration of memory subsystems at 3nm also considers the impact of advanced packaging solutions. Heterogeneous integration through chiplets offers alternatives to traditional monolithic designs, especially beneficial for analog circuits that can remain at optimal nodes without requiring scaling. Furthermore, the implementation of high-speed interfaces between dies often proves more

Figure 3. CMOS Scaling for the 5 nm Node and Beyond

efficient than routing signals across large monolithic chips through increasingly narrow interconnects.

# 4. Neural Processing Unit Design

Neural processing units stand at the forefront of AI chip advancement, with recent developments showcasing remarkable improvements in computational efficiency. The WSE-2, currently the largest chip ever constructed, demonstrates 123X more compute cores alongside 1000X more high performance on-chip memory [37].

# 4.1 Matrix Multiplication Units

Matrix multiplication units form the cornerstone of modern AI accelerators, as evidenced in recent architectural innovations. The following table illustrates the evolution of matrix computation capabilities as given in Table 7:

| Processor Type | Matrix Math Engines | Tensor Cores | Performance (FP8) |

|----------------|---------------------|--------------|-------------------|

| Gaudi 2        | 2                   | 24           | 917 TFLOPS        |

| Gaudi 3        | 4                   | 32           | 1835 TFLOPS       |

Table 7. Matrix Multiplication Units

Intel's Gaudi 3 architecture exemplifies these advancements, doubling FP8 performance to 1835 TFLOPS. Notably, the BF16 performance demonstrates a 4X improvement over its predecessor. The Tensor Streaming Architecture operates as a powerful single-threaded streaming processor, utilizing an instruction set specifically designed for tensor manipulation [38].

# 4.2 Weight Storage Optimization

Weight storage optimization emerges as a critical factor in AI chip efficiency. The following configuration table presents current memory hierarchies in advanced AI processors as given in Table 8:

| Memory Type | Capacity | Bandwidth | Application     |

|-------------|----------|-----------|-----------------|

| SRAM        | 96MB     | 12.8TB/s  | On-chip Cache   |

| НВМ2е       | 128GB    | 3.7TB/s   | Weight Storage  |

| LPDDR4      | 16GB     | Variable  | External Memory |

Table 8. Weight Storage Optimization

The implementation of high-bandwidth memory proves essential, albeit with certain limitations. Current designs utilize HBM2e memory controllers, supporting 16GB stacks clocked at 3.7Gbps/pin. Each processing die incorporates 4 HBM2e PHYs, resulting in 8 total memory stacks.

The Envise Chip exemplifies efficient memory management with 500MB of SRAM dedicated to neural network execution, eliminating the need for external memory access. Additionally, it incorporates a 400Gbps Lightmatter interconnect fabric, enabling large-model scale-out capabilities.

Recent developments in the Dimensity 9400 showcase the industry's focus on GenAI performance. The chipset's 8th-generation NPU introduces pioneering features, including on-device LoRA training support. This advancement yields up to 80% faster large language model performance alongside 35% enhanced power efficiency [39, 40].

The Cardinal SN10 RDU, manufactured on TSMC's N7 process, introduces an innovative array of reconfigurable nodes for switching, data, and storage operations. This architecture enables in-the-loop training alongside model reclassification during inference-with-training workloads.

The integration of these components requires sophisticated interconnect solutions. The on-wafer interconnect delivers 220 Pb/s bandwidth between cores, representing 45,000X improvement over traditional graphic processors. This enhancement facilitates faster deep learning operations while maintaining minimal power consumption.

# 5. Signal Integrity Solutions

Signal integrity emerges as a fundamental challenge in 3nm chip design, primarily because of process-technology scaling and diminishing spacing between adjacent interconnects. The coupling capacitance between wires increases substantially, leading to complex signal behavior that demands innovative solutions [41, 42, 43].

# 5.1 Cross-talk Mitigation Techniques

At 3nm, cross-talk presents unprecedented challenges as signals influence neighboring wires through capacitive coupling. The relationship between aggressors and victims demonstrates the following characteristics as given in Table 9:

| Parameter            | Impact Level | Mitigation Method   | Application     |

|----------------------|--------------|---------------------|-----------------|

| Coupling Capacitance | High         | Shielding Tunnels   | On-chip Cache   |

| Signal Transition    | Medium       | Timing Optimization | Weight Storage  |

| Victim Response      | Critical     | Layout Spacing      | External Memory |

Table 9. Cross-talk Mitigation Techniques

Recent studies indicate that approximately 90% of voltage drop on a given instance stems from

switching of aggressor neighbor instances. The implementation of shielding tunnel structures reduces flux crosstalk by nearly a factor of 10, achieving levels of 0.1-0.2%.

#### 5.2 Clock Distribution Networks

Clock distribution presents unique challenges at 3nm, consuming between 30-40% of total power usage. The clock network architecture incorporates sophisticated features as given in Table 10:

| Feature       | Specification | Benefit              | Application     |

|---------------|---------------|----------------------|-----------------|

| Local Buffers | Distributed   | Signal Amplification | On-chip Cache   |

| Global Clock  | Hierarchical  | Reduced Skew         | Weight Storage  |

| Power Usage   | 30-40%        | System Efficiency    | External Memory |

Table 10. Clock Distribution Networks

The Aeonic Generate<sup>™</sup> Clock Generation Module (CGM) on TSMC's 3nm process introduces programmable and synthesizable clock generation capabilities. This advancement enables feature-rich clock distribution alongside architectural innovations for enhanced system performance.

## 5.3 Power Grid Design

Power grid implementation at 3nm requires careful consideration of voltage stability and current distribution. Indeed, at advanced nodes, approximately 90% of voltage drop originates from neighboring instances. The power delivery network must account for:

The emergence of second and third-order effects becomes particularly significant at 3nm, necessitating careful attention to inductance effects. Consequently, exotic metals at lower metallization levels introduce higher resistance, making inductance a critical consideration rather than an ignorable factor [44].

Recent implementations demonstrate that clock signals begin acting as electromagnetic emitters, coupling with nearby wires possessing the correct orientation. Therefore, power grid design must incorporate sophisticated electromagnetic interference (EMI) mitigation techniques.

The integration of Quality of Service (QoS) management determines workload priorities and assigns processing resources in real-time. This approach enables dynamic adjustment of power delivery based on computational demands. Furthermore, the automotive-qualified N3A 3nm process showcases a 30-35% reduction in power consumption alongside higher integration capabilities.

Glitch power emerges as another critical consideration, potentially consuming up to 40% of total power in a chip. The implementation of glitch-aware vector generation utilizing RTL simulation provides essential optimization capabilities. Additionally, delay-aware SAIF from RTL simulation on various netlist outputs enables comprehensive power analysis and optimization [45].

# 6. Manufacturing Process Control

Manufacturing precision at 3nm demands sophisticated process control mechanisms, as a single misplaced atom can affect chip performance. At this scale, wafer inspection costs reach USD 20,000 per unit, making efficient defect detection crucial for maintaining production viability.

#### 6.1 Defect Detection Methods

Advanced inspection systems utilize both optical and electron beam technologies for comprehensive defect analysis. The relationship between inspection methods and their capabilities demonstrates

distinct characteristics as given in Table 11:

| Inspection Type | Resolution | Speed  | Application      |

|-----------------|------------|--------|------------------|

| Optical Systems | Standard   | High   | Surface Defects  |

| E-beam Systems  | Superior   | Low    | Deep Structure   |

| Multi-beam      | Enhanced   | Medium | Complex Patterns |

Table 11. Defect Detection Methods

ASML's innovative nine-beam inspection tool marks a significant advancement in defect detection capabilities. Simultaneously, unpatterned wafer inspection systems focus primarily on bare wafer examination alongside front-end manufacturing processes.

The implementation of machine learning algorithms enhances defect recognition rates through CNN-based image processing methods. This advancement proves particularly valuable for identifying irregular defects that traditional algorithms might overlook [46].

# 6.2 Yield Optimization Strategies

Yield management at 3nm presents unprecedented challenges, with manufacturers striving to achieve a minimum 60% yield rate for mass production efficiency. The correlation between various optimization parameters showcases critical relationships as given in Table 12:

| Parameter           | Target Value | Impact Factor        |

|---------------------|--------------|----------------------|

| Defect Rate         | Below 40%    | Production Viability |

| Yield Target        | 60%          | Economic Feasibility |

| Alignment Precision | Atomic Scale | Performance Impact   |

Table 12. Yield Optimization Strategies

Automated visual inspection systems expedite large batch examinations, offering substantial time savings versus manual methods. Through advanced imaging capabilities, these systems detect subtle surface quality variations beyond human visual perception.

The implementation of continuous feedback mechanisms ensures immediate detection alongside resolution of anomalies. Machine learning enhances inspection by analyzing defect data patterns, enabling manufacturers to swiftly respond to emerging defect types [47].

Overlay precision alongside alignment accuracy become increasingly critical at 3nm, where traditional alignment methods prove inadequate. The margin for error virtually disappears, requiring unprecedented precision in layer alignment.

TSMC's approach emphasizes building robust in-house R&D capabilities, alongside maintaining comprehensive process technology portfolios. This strategy enables rapid response to manufacturing challenges through internal expertise.

The integration of real-time process control alongside integrated data analytics empowers immediate adjustments. These systems effectively reduce false positive rates by approximately 90%, minimizing material waste alongside streamlining operations [48].

Effective wafer preparation emerges as fundamental for ensuring subsequent inspections reflect genuine manufacturing defects. This preparatory phase sets the foundation for accurate defect detection, preventing external contaminants from masking actual manufacturing issues.

The semiconductor industry implements two primary inspection methodologies: Automatic Optic Inspection (AOI) alongside Scanning Electron Microscope (SEM) examination. AOI systems offer rapid detection through optical principles, utilizing various illumination techniques including bright field, dark field, alongside transmission field approaches.

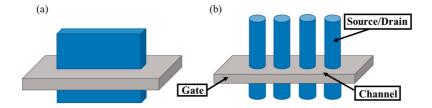

## 7. Performance Verification Methods

Performance verification at 3nm introduces sophisticated testing methodologies, as chip complexity alongside demand for performance continue increasing. Automated test equipment (ATE) evolves to meet these challenges through enhanced precision alongside reduced testing costs as in Fig. 4.

Figure 4. State of the Art and Future Perspectives

# 7.1 Functional Testing Approaches

The semiconductor testing landscape incorporates both traditional functional testing alongside structural verification methods. The correlation between testing approaches alongside their effectiveness demonstrates distinct characteristics as given in Table 13:

| Testing Method     | Coverage        | Application          | Precision     |

|--------------------|-----------------|----------------------|---------------|

| Structural Testing | Component Level | Design Integrity     | High          |

| System Level Test  | Full System     | Real Environment     | Comprehensive |

| Built-in Self-Test | On-chip         | Runtime Verification | Continuous    |

Table 13. Functional Testing Approaches

System-level testing emerges as mandatory within test flows, primarily for complex devices such as AI chips alongside processors. This comprehensive methodology validates functionality, performance, alongside interoperability within intended system environments [48].

The implementation of built-in self-test (BIST) mechanisms enables thorough verification throughout operational cycles. These sophisticated techniques provide deeper insights into chip design alongside manufacturing process integrity.

Advanced data analytics through AI integration offers innovative approaches toward analyzing vast amounts of test data, identifying patterns, alongside optimizing testing parameters in real-time. This advancement enables continuous yield improvement throughout semiconductor lifecycles.

# 7.2 Speed Grade Classification

Speed grade classification requires meticulous evaluation of chip performance characteristics. The relationship between various performance metrics showcases critical correlations as given in Table 14:

| Performance Metric | Improvement | Process Node | Precision     |

|--------------------|-------------|--------------|---------------|

| N3E Performance    | 10-15%      | vs N5        | High          |

| N3P Enhancement    | 5%          | vs N3E       | Comprehensive |

| N3X Speed Gain     | 5%          | vs N3P       | Continuous    |

Table 14. Speed Grade Classification

TSMC's N3E process technology demonstrates remarkable achievements, offering 10-15% higher performance at identical power levels. Additionally, N3P continues optimizing transistor characteristics, enabling either 5% increased performance at equivalent leakage or 5-10% reduced power at identical clock speeds as in Fig. 5.

Figure 5. Controlling the Carrier Injection Efficiency

The evolution toward N3X projects minimum 5% higher clock speeds compared to N3P, accomplished through enhanced voltage tolerance. Nevertheless, this advancement introduces approximately 3.5 times higher leakage, necessitating careful consideration within design trade-offs.

Comprehensive validation ensures optimal performance under diverse conditions, focusing primarily on power density management alongside thermal hotspot minimization. This thorough approach guarantees reliable operation across varying workload scenarios.

The integration of system-level testing alongside traditional ATE methods creates flexible strategies for comprehensive verification. These combined methodologies enable efficient handling of real-time, diverse, alongside distributed AI workloads.

Manufacturers evaluate semiconductor devices under real-world conditions, ensuring thorough validation of performance alongside interactions with hardware alongside software components. This approach proves particularly vital for advanced system-on-chip (SoC) alongside system-in-package (SiP) designs, identifying potential issues early within production cycles.

The implementation of advanced testing methodologies addresses increasing test sensitivity requirements at smaller geometries. These sophisticated approaches maintain high-quality yields through enhanced precision alongside accuracy within testing procedures as in Fig. 6.

Figure 6. Chiplet Heterogeneous Integration Technology

# 8. Thermal Management Systems

Thermal management stands at the forefront of 3nm AI chip design, as smaller transistors packed densely generate substantial heat despite their individual power efficiency. Although these miniature transistors consume less energy, their increased density results in heightened thermal challenges.

## 8.1 Heat Dissipation Techniques

The correlation between cooling methods alongside their effectiveness demonstrates distinct characteristics as given in Table 15:

| Cooling Method        | Heat Removal Capacity     | Energy Efficiency |

|-----------------------|---------------------------|-------------------|

| Forced Air            | Up to 50W/cm <sup>2</sup> | Standard          |

| Direct-to-Chip Liquid | 160kW                     | High              |

| Immersion Cooling     | Maximum                   | Superior          |

Table 15. Heat Dissipation Techniques

Single-phase liquid cooling emerges as an efficient solution, offering 3,600 times better heat transfer capacity per volume alongside water. Through direct-to-chip cooling, liquid flows through cold plate channels attached to the chip's heat spreader via thermal interface.

Two-phase cooling operations demonstrate superior performance by allowing fluorocarbon-based liquids to evaporate upon heat absorption, afterward recondensing at heat exchangers. This innovative approach proves essential as data centers now consume over 100MW, with cooling accounting for approximately one-third of total energy usage as given in Table 16:

| Temperature Range | Cooling Solution  | Application        |

|-------------------|-------------------|--------------------|

| Up to 35°C        | Air Cooling       | Standard Computing |

| 17°C - 45°C       | Liquid Cooling    | Al Accelerators    |

| Above 45°C        | Two-Phase Systems | High-Performance   |

Table 16. Two-phase cooling operations

## 8.2 Temperature Monitoring Circuits

Advanced Process-Voltage-Temperature (PVT) monitoring systems incorporate distributed thermal sensors enabling precise thermal analysis. These sophisticated systems include as given in Table 17:

| Advancement      | Impact              | Challenge          |

|------------------|---------------------|--------------------|

| GAA Architecture | 45% Power Reduction | Quantum Effects    |

| HBM Integration  | 3.7TB/s Bandwidth   | Thermal Management |

| NPU Design       | 1835 TFLOPS         | Signal Integrity   |

| Process Control  | 60% Yield Target    | Defect Detection   |

Table 17. Temperature Monitoring Circuits

The fourth-generation PVT controller manages multiple sensor instantiations, providing comprehensive thermal oversight. Catastrophic trip sensors offer programmable protection against thermal runaway, alongside thermal diodes measuring die temperature even during powered-off states.

Recent findings highlight concerning thermal issues in devices utilizing TSMC's 3nm process. Surface temperatures reaching 48°C during intensive tasks necessitate immediate throttling, potentially affecting device lifespan alongside battery integrity. This thermal challenge primarily stems from energy losses through leakage current, suggesting potential process refinement requirements.

The implementation of JetCool's direct-to-chip liquid cooling modules utilizes small fluid jet arrays targeting processor hotspots. This precision approach transforms cooling performance at device level, although system fans remain necessary for peripheral component cooling as given in Table 18:

| Cooling Method | Capacity            | Application        |

|----------------|---------------------|--------------------|

| Two-Phase      | Maximum             | Data Centers       |

| Direct Liquid  | 160kW               | Al Accelerators    |

| Forced Air     | 50W/cm <sup>2</sup> | Standard Computing |

Table 18. Temperature Monitoring Circuits

Vertical power delivery concepts align cooling solutions with DC/DC converters positioned directly below processors, minimizing voltage drops. Nevertheless, thermal resistance between chips alongside cold plates presents ongoing challenges, requiring precision surface flatness alongside high-performance thermal interface materials.

The modular design of modern thermal management systems provides highly configurable PVT monitor fabrics based on target applications. These advanced solutions prove increasingly critical for successful advanced node chip design, driven by escalating design complexity alongside device gate density.

# 9. Conclusion

Modern 3nm AI chip design represents remarkable technological progress through sophisticated engineering solutions. Manufacturing capabilities now enable billions of transistors on single chips while maintaining optimal power, performance, and area metrics. Thermal management solutions prove essential as power density increases with transistor scaling. Direct-to-chip liquid cooling systems demonstrate superior heat dissipation capabilities, managing temperatures effectively across complex AI architectures. Signal integrity solutions address cross-talk challenges through innovative shielding techniques. Manufacturing process control systems utilize advanced inspection methods, ensuring consistent quality across production runs. Performance verification methods combine structural testing alongside system-level validation, guaranteeing reliable operation under diverse conditions. These technological advancements establish strong foundations for future AI chip development. Continuous refinement of design methodologies, coupled with emerging materials and manufacturing techniques, promises enhanced capabilities for next-generation computing systems.

# References

- [1] Yuan Taur and Tak H Ning. *Fundamentals of modern VLSI devices*. Cambridge university press, 2021.

- [2] M Michael Vai. VLSI design. CRC press, 2017.

- [3] Filip Kocina and Jiří Kunovský. "Advanced VLSI Circuits Simulation". In: 2017 International Conference on High Performance Computing & Simulation (HPCS). IEEE. 2017, pp. 526–533.

- [4] Vidisha Khetarpal, Lipika Gupta, Raman Dhand, and Preeti Sharma. "Machine Learning Techniques for VLSI Circuit Design: A Review". In: *International Conference on Intelligent Systems Design and Applications*. Springer. 2023, pp. 191–199.

- [5] Oliver Ava, Muhammad Oscar, and Tommy George. "The Impact and Prevention of Latch-up in CMOS in VLSI Design". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 1.1 (2020), pp. 1–13.

- [6] Jeetendra Singh, Balwant Raj, and Monirujjaman Khan. "Role of high-performance VLSI in the advancement of healthcare systems". In: *Advanced Circuits and Systems for Healthcare and Security Applications*. CRC Press, 2022, pp. 147–160.

- [7] Tomasz Wojcicki. VLSI: Circuits for emerging applications. CRC Press, 2017.

- [8] Cherry Bhargava and Gaurav Mani Khanal. Advanced VLSI Technology: Technical Questions with Solutions. River Publishers, 2022.

- [9] Saptarshi Das, Amritanand Sebastian, Eric Pop, Connor J McClellan, Aaron D Franklin, Tibor Grasser, Theresia Knobloch, Yury Illarionov, Ashish V Penumatcha, Joerg Appenzeller, et al. "Transistors based on two-dimensional materials for future integrated circuits". In: *Nature Electronics* 4.11 (2021), pp. 786–799.

- [10] Nakamura Shuto, Akari Chiyo, Himari Ken, and Sato Tanaka. "Quantum Materials to the Pioneering Future of Computing and Communication". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 1.1 (2020), pp. 50–62.

- [11] Suman Lata Tripathi, Sobhit Saxena, Sanjeet Kumar Sinha, and Govind Singh Patel. *Digital VLSI design and simulation with Verilog*. Wiley Online Library, 2022.

- [12] Sudhakar Alluri, B Balaji, and Ch Cury. "Low power, high speed VLSI circuits in 16nm technology". In: *AIP Conference Proceedings*. Vol. 2358. 1. AIP Publishing. 2021.

- [13] Takahiro Hanyu, Tetsuo Endoh, Daisuke Suzuki, Hiroki Koike, Yitao Ma, Naoya Onizawa, Masanori Natsui, Shoji Ikeda, and Hideo Ohno. "Standby-power-free integrated circuits using MTJ-based VLSI computing". In: *Proceedings of the IEEE* 104.10 (2016), pp. 1844–1863.

- [14] Andrew B Kahng, Lutong Wang, and Bangqi Xu. "TritonRoute: An initial detailed router for advanced VLSI technologies". In: 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD). IEEE. 2018, pp. 1–8.

- [15] Alexandre Gabriel, Claude Charles, Louis Andre, and Charlotte Antoine. "Navigating the Future of Wearable Devices with Flexible Electronics". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 1.2 (2020), pp. 63–72.

- [16] Sergey K Tolpygo, Vladimir Bolkhovsky, Terence J Weir, Alex Wynn, Daniel E Oates, Leonard M Johnson, and Mark A Gouker. "Advanced fabrication processes for superconducting very large-scale integrated circuits". In: *IEEE Transactions on Applied Superconductivity* 26.3 (2016), pp. 1–10.

- [17] Deepthi Amuru, Andleeb Zahra, Harsha V Vudumula, Pavan K Cherupally, Sushanth R Gurram, Amir Ahmad, and Zia Abbas. "AI/ML algorithms and applications in VLSI design and technology". In: *Integration* 93 (2023), p. 102048.

- [18] Vamshi Krishna Kambhampati, UP Shikohabad, Shaik Saidulu, and PA Saleem. "Evolution of low power digital VLSI system design using cmos circuit". In: *GIS science journal* 8.5 (2021), pp. 1638–1650.

- [19] Ayush Tiwari and Mrs Rajani Bisht. "Leakage Power Reduction in CMOS VLSI Circuits using Advance Leakage Reduction Method". In: *International Journal for Research in Applied Science and Engineering Technology* 9 (2021), pp. 962–966.

- [20] Adrichem De Jong, Mark Jansen, Jeffrey Van Dijk, and Johannes Meyer. "Analysis of Innovative Practices in Advanced Materials and Structural Engineering". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 2.1 (2021), pp. 178–188.

- [21] Pietro Nannipieri, Stefano Di Matteo, Luca Baldanzi, Luca Crocetti, Luca Zulberti, Sergio Saponara, and Luca Fanucci. "VLSI design of Advanced-Features AES CryptoProcessor in the framework of the European Processor Initiative". In: *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* 30.2 (2021), pp. 177–186.

- [22] Jody Maick Matos, Jordi Carrabina, and Andre Reis. "Efficiently mapping VLSI circuits with simple cells". In: *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 38.4 (2018), pp. 692–704.

- [23] BT Geetha, B Padmavathi, and V Perumal. "Design methodologies and circuit optimization techniques for low power CMOS VLSI design". In: 2017 IEEE International Conference on Power, Control, Signals and Instrumentation Engineering (ICPCSI). IEEE. 2017, pp. 1759–1763.

- [24] Theodore Elijah, James Clarence, Benjamin Anthony, and Christopher William. "The Journey and Potential of Organ-on-a-Chip Technology". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 2.2 (2021), pp. 211–223.

- [25] Anirban Sengupta, Vipul Kumar Mishra, David Pan, Yier Jin, Theocharis Theocharides, Prasun Ghosal, Mayukh Sarkar, Amlan Ganguly, Naseef Mansoor, Md Shahriar Shamim, et al. VLSI Circuits and Systems Letter. 2019.

- [26] Chuan Zhang, Yuan-Hao Huang, Farhana Sheikh, and Zhongfeng Wang. "Advanced baseband processing algorithms, circuits, and implementations for 5G communication". In: *IEEE Journal on Emerging and Selected Topics in Circuits and Systems* 7.4 (2017), pp. 477–490.

- [27] Yihang Qiu, Yan Xing, Xin Zheng, Peng Gao, Shuting Cai, and Xiaoming Xiong. "Progress of placement optimization for accelerating VLSI physical design". In: *Electronics* 12.2 (2023), p. 337.

- [28] P Sasipriya and VS Kanchana Bhaaskaran. "Design of low power VLSI circuits using two phase adiabatic dynamic logic (2PADL)". In: *Journal of Circuits, Systems and Computers* 27.04 (2018), p. 1850052.

- [29] Valdemar Johansen, Malthe Rasmussen, and Arne Knudsen. "Dielectric Constants and Their Role in Plasma Simulation". In: *Fusion of Multidisciplinary Research, An International Journal (FMR)* 3.1 (2022), pp. 248–260.

- [30] Sanjay Vidhyadharan, Ramakant Yadav, Simhadri Hariprasad, and Surya Shankar Dan. "An advanced adiabatic logic using Gate Overlap Tunnel FET (GOTFET) devices for ultra-low power VLSI sensor applications". In: *Analog Integrated Circuits and Signal Processing* 102.1 (2020), pp. 111–123.

- [31] Suryakanta Nayak and Mrutyunjaya Panda. "Realization of VLSI circuit partitioning using advanced genetic algorithm". In: *Solid State Technology* 63.5 (2020), pp. 9129–9145.

- [32] Fernanda Hernández, Leonardo Sánchez, Gabriela González, and Andrés Ramírez. "Revolutionizing CMOS VLSI with Innovative Memory Design Techniques". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 3.2 (2022), pp. 366–379.

- [33] Rassul Bairamkulov and Eby Friedman. "Graphs in vlsi circuits and systems". In: *Graphs in VLSI*. Springer, 2022, pp. 59–100.

- [34] Peng Zou, Xiqiong Bai, Yingjie Wu, Lifeng Wu, and Jianli Chen. "An effective detailed routing algorithm considering advanced VLSI technologies". In: 2019 IEEE 13th International Conference on ASIC (ASICON). IEEE. 2019, pp. 1–4.

- [35] Shira Rubin, Daniel Mizrachi, Noam Friedman, Hila Edri, and Tamar Golan. "The World of Advanced Thin Films: Design, Fabrication, and Applications". In: *Fusion of Multidisciplinary Research, An International Journal (FMR)* 4.1 (2023), pp. 393–406.

- [36] Kuruva Lakshmanna, Fahimuddin Shaik, Vinit Kumar Gunjan, Ninni Singh, Gautam Kumar, and R Mahammad Shafi. "Perimeter degree technique for the reduction of routing congestion during placement in physical design of VLSI circuits". In: Complexity 2022.1 (2022), p. 8658770.

- [37] Samar K Saha. FinFET devices for VLSI circuits and systems. CRC Press, 2020.

- [38] T Suguna and M Janaki Rani. "Survey on power optimization techniques for low power VLSI circuit in deep submicron technology". In: *International Journal of VLSI design and Communication Systems* 9.1 (2018), pp. 1–15.

- [39] Elliot Greenwald, Matthew R Masters, and Nitish V Thakor. "Implantable neurotechnologies: bidirectional neural interfaces—applications and VLSI circuit implementations". In: *Medical & biological engineering & computing* 54 (2016), pp. 1–17.

- [40] Ibrahim M Elfadel, Duane S Boning, and Xin Li. *Machine learning in VLSI computer-aided design*. Springer, 2019.

- [41] Jitesh R Shinde, Suresh S Salankar, and Shilpa J Shinde. "Multi-objective optimization domino techniques for VLSI circuit". In: 2016 International Conference on Advances in Computing, Communications and Informatics (ICACCI). IEEE. 2016, pp. 2126–2130.

- [42] Bernhard Sell, S An, J Armstrong, D Bahr, B Bains, R Bambery, K Bang, D Basu, S Bendapudi, D Bergstrom, et al. "Intel 4 CMOS technology featuring advanced FinFET transistors optimized for high density and high-performance computing". In: 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). IEEE. 2022, pp. 282–283.

- [43] Anastasia Klymenko, Snizhana Shevchenko, Rostislav Marchenko, and Dmitriy Tkachenko. "Electrode Batteries: Organic Material's influence on Lithium-Ion Battery Performance". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 4.2 (2023), pp. 458–470.

- [44] Brajesh Kumar Kaushik. Nanoelectronics: Devices, Circuits and Systems. Elsevier, 2018.

- [45] Rassul Bairamkulov and Eby G Friedman. *Graphs in VLSI*. Springer, 2023.

- [46] Angsuman Sarkar, Swapnadip De, Manash Chanda, and Chandan Kumar Sarkar. *Low power VLSI design: fundamentals.* Walter de Gruyter GmbH & Co KG, 2016.

- [47] Ankur Kumar, Sajal Agarwal, Vikrant Varshnay, Varun Mishra, Yogesh Kumar Verma, and Suman Lata Tripathi. Opto-VLSI Devices and Circuits for Biomedical and Healthcare Applications. CRC Press, 2023.

[48] Gage Hills, Marie Garcia Bardon, Gerben Doornbos, Dmitry Yakimets, Pieter Schuddinck, Rogier Baert, Doyoung Jang, Luca Mattii, Syed Muhammed Yasser Sherazi, Dimitrios Rodopoulos, et al. "Understanding energy efficiency benefits of carbon nanotube field-effect transistors for digital VLSI". In: *IEEE Transactions on Nanotechnology* 17.6 (2018), pp. 1259–1269.