#### **ARTICLE**

# Breaking Physics Limits: How 2nm Chip Technology Powers Next-Gen 3D ICs

Q. Zhang,\* H. Deng, K. Song, and Xi Lee

Department of Electronics Engineering, Chang Gung University, Taoyuan 333, Taiwan

\*Corresponding author: zhangq65@mail.cgu.edu.tw

(Received: 17 September 2024; Revised: 23 December 2024; Accepted: 01 February 2025; Published: 16 February 2025)

#### **Abstract**

The breakthrough 2nm chip technology represents a significant leap in semiconductor innovation, promising enhanced performance and reduced power consumption across multiple industries. While current chip technologies have served us well, the 2nm process is set to deliver a remarkable 12% boost in energy efficiency, fundamentally transforming how we design and build next-generation electronic devices. This advancement comes at a crucial time, as we witness unprecedented demands in consumer electronics, automotive systems, healthcare devices, and artificial intelligence applications. Additionally, the recent launch of Imec's design pathfinding PDK in February 2024 has opened new possibilities for system research and training. With TSMC's planned production rollout in 2025, we stand at the threshold of a new era in semiconductor manufacturing. In this comprehensive guide, we will explore the intricate details of 2nm chip technology, from its revolutionary architecture to its practical applications in 3D ICs. We will examine how this technology incorporates advanced features like nanosheet devices and backside power grids, ultimately shaping the future of high-performance computing and mobile devices.

Keywords: 2nm Chip Technology;3D ICs Advanced Semiconductors; Chip Design; Energy Efficiency; Moore's Law

Abbreviations: EUV: Extreme ultraviolet, FEC: Forward Error Correction, GAA: Gate-All-Around, TSV: Through-silicon via

# 1. Understanding 2nm Chip Architecture

TSMC's groundbreaking 2nm process node marks a fundamental shift in semiconductor design, incorporating advanced nanosheet transistors and innovative power delivery systems. Furthermore, this technological milestone introduces significant improvements in transistor density and overall chip efficiency [1, 2, 3].

# 1.1 Core Components of 2nm Process

The foundation of 2nm technology rests on a sophisticated architecture that achieves a remarkable 1.15-times increase in transistor density. Consequently, this advancement enables manufacturers to optimize node performance by fitting different logic cells in minimal areas through N2 NanoFlex technology.

The architecture comprises multiple critical layers, specifically designed for optimal performance as in Table 1 [4, 5, 6]:

The interconnect system utilizes sophisticated copper wiring schemes, connected through precisely

<sup>© 2025</sup> The Author(s). Published by Fusion of Multidisciplinary Research, An International Journal (FMR), Netherlands, under the (Creative Commons Attribution 4.0 International License (CC BY 4.0)

| Component            | Function                                                |

|----------------------|---------------------------------------------------------|

| Transistor Layer     | Forms the base switching mechanism                      |

| Middle-of-Line (MOL) | Contains tiny contact structures connecting transistors |

| Interconnect Layers  | 10-15 layers of copper wiring schemes                   |

Table 1. Gate Length Scaling Challenges at 3nm

engineered vias. Moreover, the implementation of buried power rails in the transistor structure helps free up routing resources, thus enhancing overall efficiency [7].

## 1.2 Gate-All-Around Transistor Design

The 2nm process introduces a revolutionary Gate-All-Around (GAA) transistor architecture that surpasses traditional FinFET technology. Specifically, the GAA design wraps the gate around all four sides of the transistor, enabling superior control over current flow as in Table 2 [8, 9]:

| GAA Features     | Benefits                     |

|------------------|------------------------------|

| Nanosheet Stack  | Enhanced current control     |

| Silicon Ribbons  | Precise parameter tuning     |

| Four-sided Gate  | Better electrostatic control |

| Adjustable Width | Optimized power consumption  |

Table 2. Gate Length Scaling Challenges at 3nm

The nanosheet transistor structure consists of thin, alternating layers of silicon and silicon germanium, forming the transistor channel. Subsequently, gate material surrounds this nanosheet channel on all sides, offering unprecedented control over current flow and reduced leakage.

#### 1.3 Power Efficiency Improvements

The 2nm process node demonstrates remarkable advancements in power efficiency through several innovative features. First, TSMC's implementation shows a 15% increase in performance coupled with up to 30% reduction in power consumption.

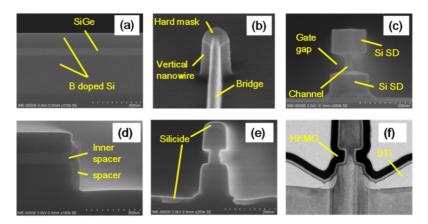

The power delivery network incorporates several groundbreaking elements as in Fig. 1 [10, 11].

- Backside Power Delivery: This revolutionary approach transfers power distribution to the wafer's underside, reducing resistance to the transistor source. As a result, the metal scheme becomes simplified, allowing resources to be reallocated for optimal signal routing.

- Voltage Distribution Systems: The implementation of advanced voltage distribution mechanisms

helps achieve a 15-20% improvement in power usage for high-performance designs. Therefore,

this enhancement particularly benefits designs requiring substantial power redistribution across

the die.

The transition from traditional FinFET to dedicated N2 "nanosheet" technology enables manufacturers to fine-tune parameters based on specific process requirements. Particularly, the drive current in GAA devices can be adjusted to optimal values by varying the width, offering superior power management compared to FinFET's fixed fin-based approach [13].

The architecture also incorporates a multi-threshold-voltage device offering, featuring leakage levels spanning three orders of magnitude. Correspondingly, this advancement allows device manufactur-

Figure 1. SEM micrographs [12]

ers to select performance levels that align with specific chip architecture requirements. Through these innovations, the 2nm process achieves approximately 75% power savings while maintaining consistent performance levels [14, 15].

# 2. Materials Science Breakthroughs

Materials science innovations stand at the forefront of enabling 2nm chip manufacturing, marking a decisive shift from traditional semiconductor materials. Indeed, the industry's relentless pursuit of smaller, faster chips has necessitated groundbreaking developments in both conductive and insulating materials.

# 2.1 Advanced Silicon Compounds

The evolution of silicon-based compounds has reached new heights with the introduction of multilayer nanosheet structures. These structures incorporate alternating layers of silicon and silicon germanium, enabling precise control over transistor characteristics. The following table illustrates the key material advancements as in Table 3 [16]:

| Material Innovation       | Performance Impact                      |

|---------------------------|-----------------------------------------|

| Binary Metal Liner (RuCo) | Reduces liner thickness by 33%          |

| Ruthenium-Enhanced Wiring | Decreases resistance by 25%             |

| Single-grain Metal        | Enhances low-resistance via performance |

| Direct-etched Metal       | Improves interconnect reliability       |

Table 3. Gate Length Scaling Challenges at 3nm

The implementation of ruthenium in high-volume production represents a significant milestone in metallization technology. This advancement primarily addresses the challenges of copper wiring at the 2nm node, where traditional approaches face physical scaling limitations.

The material engineering process now encompasses sophisticated techniques for creating void-free copper wires. Through an Integrated Materials Solution (IMS), manufacturers combine six distinct technologies to achieve precise layering. The following table outlines the critical material parameters as in Table 4 [17, 18]:

| Material Parameter     | Technical Specification        |

|------------------------|--------------------------------|

| Metal Pitch Range      | 24nm to 21nm                   |

| Gate Length            | 12nm with three silicon layers |

| N-P Space              | Less than 40nm                 |

| Sheet-to-Sheet Spacing | Sub-1nm thickness              |

Table 4. Gate Length Scaling Challenges at 3nm

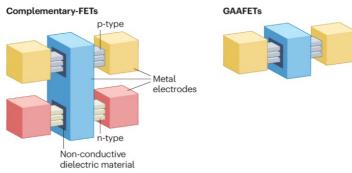

#### 2.2 Novel Insulation Materials

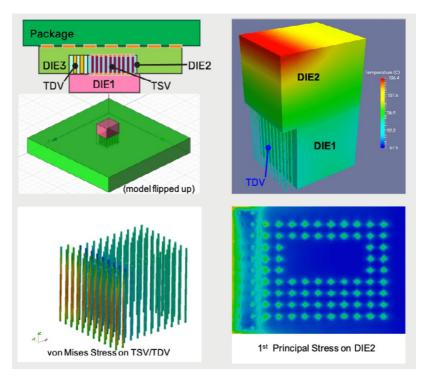

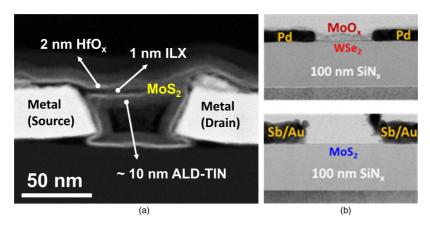

The development of advanced insulation materials has become increasingly crucial for managing electrical interference and power consumption. The industry has witnessed remarkable progress in dielectric materials, moving beyond traditional low-k solutions toward more sophisticated compounds. as in Fig. 2 [19, 20].

Figure 2. Thermal-mechanical co-simulation of 3D-IC design [21]

A significant breakthrough emerged with the enhancement of Black Diamond material, which now offers an even lower k-value for 2nm applications. This advancement addresses two critical challenges as in Table 5 [22, 23]:

The introduction of air gap technology represents another milestone in insulation innovation. Air, possessing the lowest k-value (1.00059) among all materials, offers unprecedented potential for reducing dielectric permittivity. The implementation involves [24, 25]:

- · Advanced electrospinning technology for air-gap formation

- · Integration of polyimide materials

| Insulation Challenge    | Solution Implementation                     |

|-------------------------|---------------------------------------------|

| Electrical Interference | Enhanced low-k dielectric material          |

| Structural Integrity    | Strengthened chip structure for 3D stacking |

Table 5. Gate Length Scaling Challenges at 3nm

### · Precise control of gap dimensions

The barriers and liners in modern interconnect structures now occupy significantly reduced trench volumes. Nevertheless, this reduction presents new challenges in copper deposition, necessitating innovative approaches to prevent void formation. The industry has responded by developing selective deposition techniques for via metal filling, eliminating the need for traditional liners [26].

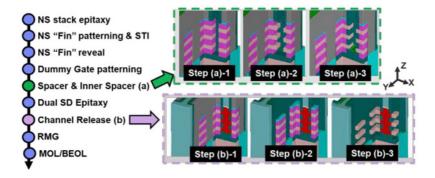

In the realm of gate dielectrics, plasma ion damage during etching has emerged as a critical concern. This challenge has led to the development of new etch processes that prevent inadvertent thickening of interfacial layers. The selective layer reduction (SLR) approach, implemented through SLR1 and SLR2 techniques, effectively addresses the undercutting issues in metal gate boundaries as in Fig. 3 [27, 28].

Figure 3. Multilayer nanosheet GAA process [29]

The integration of these material innovations has enabled unprecedented achievements in chip performance. For instance, the combination of enhanced low-k dielectrics and ruthenium-based metallization has facilitated the creation of chips that maintain structural integrity during advanced 3D stacking processes. Furthermore, the implementation of volumeless multi-Vt technology, utilizing materials less than 1nm thick, has successfully addressed the challenges of threshold voltage control in nanosheet devices [30].

# 3. Thermal Management in 2nm Technology

Power dissipation emerges as a critical challenge in 2nm chip technology, where heat management directly impacts device performance and reliability. Since power consumed by semiconductors generates heat that must be removed efficiently, thermal considerations now influence early design and packaging decisions in 2.5D and 3D packages [31, 32].

#### 3.1 Heat Distribution Patterns

The thermal landscape in 2nm chips presents unique challenges due to increased power density and physical constraints. Heat distribution varies significantly based on workload patterns, creating

dynamic temperature gradients across the chip. The following table illustrates key thermal characteristics as in Table 6 [33, 34]:

| <b>Heat Distribution Factor</b> | Impact on 2nm Chips                       |

|---------------------------------|-------------------------------------------|

| Silicon Conductivity            | 100-120 W/(m x K)                         |

| Copper Conductivity             | 400 W/(m x K)                             |

| Power Density Limit             | 1 megawatt per meter squared              |

| Temperature Impact              | Changes device electrical characteristics |

Table 6. Gate Length Scaling Challenges at 3nm

Backside power delivery notably alters the thermal landscape, doubling the heat generated on the silicon's backside. Previously stable temperatures of 50°C now potentially reach 100°C, necessitating innovative cooling approaches [35].

## 3.2 Cooling System Integration

Advanced cooling solutions have evolved beyond traditional methods to address the intense thermal demands of 2nm technology. The industry has developed a hierarchy of cooling capabilities as in Table 7 [36, 37]:

| Cooling Method            | Power Handling Capacity |

|---------------------------|-------------------------|

| Basic Heatsink            | 1 kW/m²                 |

| Fan-based Systems         | 10 kW/m²                |

| Advanced Server Equipment | 1 MW/m <sup>2</sup>     |

Table 7. Gate Length Scaling Challenges at 3nm

Microfluidics represents a promising advancement in cooling technology. Direct-bonded liquid coolers achieve thermal resistance between 0.34K/W to 0.28K/W at less than 2W pump power. However, practical implementation faces challenges including reliability concerns, maintenance requirements, and system complexity as in Fig. 4 [38].

In heterogeneous packaging, thermal management becomes increasingly complex due to dissimilar heights of individual chiplets and components. Approximately 95% of the device's total power dissipates through the package top into system-level cooling solutions. Nonetheless, this configuration often benefits thermal performance by spreading heat-generating components apart, reducing thermal crosstalk.

# 3.3 Temperature Control Mechanisms

Temperature control in 2nm chips incorporates multiple strategies to maintain optimal operating conditions. When sufficient cooling cannot be achieved, cores must be throttled or deactivated to prevent overheating. This phenomenon, known as 'dark silicon,' limits device performance as regions must remain inactive due to thermal constraints.

Heat pipes and vapor chambers utilize phase change heat transfer in closed loops, achieving thermal conductivities substantially higher than traditional materials. Liquid-cooled cold plates offer superior cooling for high power densities while maintaining a low profile, eliminating the need for extensive airflow clearance [40].

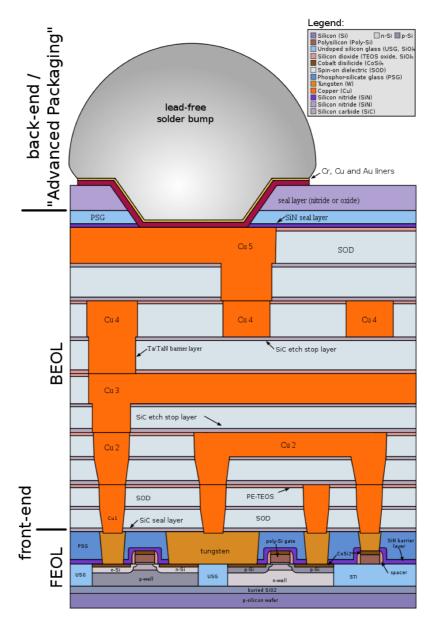

Figure 4. BEOL and FEOL [39]

Immersion cooling presents an innovative solution where devices directly contact dielectric coolant. Two-phase immersion systems maintain constant temperature across devices in the coolant bath, albeit with more complex implementation requirements. For data centers, each 1°C increase in ambient temperature translates to approximately 2% cooling cost savings.

Thermally aware component placement offers significant optimization potential. High-power components should be distributed across the package area to achieve even power distribution. This approach, alongside careful material selection and design considerations, helps optimize overall thermal performance while maintaining the structural integrity necessary for reliable operation [41, 42, 43].

# 4. Power Delivery Network Innovations

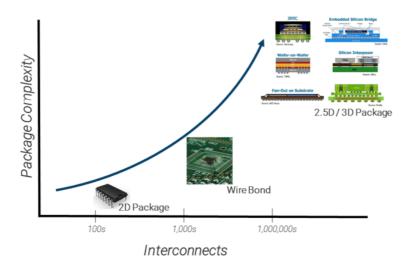

Power delivery networks in 2nm chip manufacturing have undergone a fundamental transformation, introducing groundbreaking approaches that enhance performance and efficiency. These innovations primarily focus on optimizing power distribution and minimizing voltage drops across the chip architecture as in Fig. 5) [1, 2].

Figure 5. PEEC mesh [44]

#### 4.1 Backside Power Delivery

The semiconductor industry has witnessed a paradigm shift with the introduction of backside power delivery network (BSPDN) technology. This innovative approach relocates power rails to the wafer's back, effectively removing bottlenecks between power and signal lines. The implementation of BSPDN offers substantial benefits, as shown in the following comparison as in Table 8 [45, 46]:

| Performance Metric    | Improvement     |

|-----------------------|-----------------|

| Power Efficiency      | 15-20% boost    |

| Voltage Droop         | 30% reduction   |

| Cell Utilization      | 90% achievement |

| Frequency Performance | 6% increase     |

Table 8. Gate Length Scaling Challenges at 3nm

Three distinct methodologies have emerged for implementing backside power delivery as in Table 9 [47, 48]:

The manufacturing process involves intricate steps, beginning with transistor fabrication, followed by nanoTSV etching and filling with low-resistance metals. Afterward, signal interconnects spanning M0 to M14 layers are constructed, utilizing slightly larger metal-0 lines. The wafer undergoes precise thinning, leaving approximately 500nm of silicon, essential for maintaining structural integrity.

| Approach                                  | Characteristics         | Implementation Details       |

|-------------------------------------------|-------------------------|------------------------------|

| Buried Power Rail Simplest implementation |                         | Connects via deep power rail |

| Durieu i Owei itali                       | Simplest implementation | around CMOS FETs             |

| PowerVia                                  | Advanced evolution      | Uses nanoTSVs for backside   |

| Towervia                                  | Advanced evolution      | network connection           |

| Direct Backside                           | Most sophisticated      | Enables 25% cell scaling     |

| Contacts                                  | wost sopmsticated       | reduction                    |

Table 9. Gate Length Scaling Challenges at 3nm

#### 4.2 Voltage Distribution Systems

Advanced voltage distribution mechanisms have been integrated into the 2nm process, primarily focusing on optimizing power delivery efficiency. Intel's recent PowerVia implementation demonstrated remarkable improvements in platform voltage stability. The system incorporates sophisticated metal-insulator-metal (MIM) capacitors, specifically designed to enhance power supply stability.

The voltage distribution network achieves optimal performance through several key innovations as in Table 10 [49]:

| Innovation               | Technical Impact                          |

|--------------------------|-------------------------------------------|

| Copper Line Optimization | 50% reduction in sheet resistance         |

| Via Resistance           | 50% decrease in contact resistance        |

| Power Rail Space         | 20% surface area optimization             |

| Signal Layer Efficiency  | Metal-0 pitch loosening from 30nm to 36nm |

Table 10. Gate Length Scaling Challenges at 3nm

The implementation of these advanced systems presents unique challenges, particularly in maintaining precise alignment between frontside and backside connections. Engineers must carefully manage stress buildup, which shows 62% greater tensile stress in the z-direction, concentrating at the first metal layer above the nanoTSV as in Fig. 6 [50].

Figure 6. A cross-sectional TEM of the suspended MoS2 nanosheet structure [51]

Looking ahead, the backside power delivery infrastructure will expand beyond power and global clock distribution. Future implementations might incorporate signals and BEOL devices, including capacitors. This evolution promises to further enhance chip performance while maintaining the structural integrity necessary for reliable operation.

# 5. 3D Integration Techniques

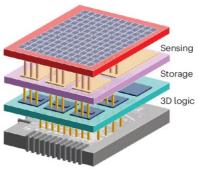

Three-dimensional integration emerges as a cornerstone of 2nm chip manufacturing, enabling unprecedented levels of functionality within compact footprints. This sophisticated approach to chip design combines multiple dies into unified systems, fundamentally changing how we construct advanced semiconductor devices.

## 5.1 Vertical Stacking Methods

Vertical integration techniques have evolved to accommodate diverse manufacturing requirements. The implementation of multi-die approaches offers superior modularity alongside enhanced cost efficiency through strategic die splitting. The following table illustrates key vertical stacking configurations as in Table 11:

| Stacking Method | Technical Characteristics    | Application Benefits   |

|-----------------|------------------------------|------------------------|

| Die-to-Die      | Pre-testing capability       | Enhanced yield control |

| Wafer-to-Wafer  | Full wafer processing        | Higher throughput      |

| Chip-to-Wafer   | Mixed technology integration | Flexible manufacturing |

Table 11. Gate Length Scaling Challenges at 3nm

The stacking process incorporates sophisticated alignment techniques, requiring precise coordination between dies. In fact, recent implementations demonstrate successful integration of up to 16 stacked ICs, marking a substantial advancement in vertical integration capabilities.

#### 5.2 Through-Silicon Via Technology

Through-silicon vias (TSVs) serve as vertical electrical connections passing through silicon wafers, enabling direct communication between stacked components. These high-performance interconnects achieve superior density compared to traditional package-on-package solutions.

Modern TSV implementations showcase remarkable versatility across different applications as in Table 12:

| TSV Application     | Dimensions             | Performance Metrics     |

|---------------------|------------------------|-------------------------|

| Image Sensors       | Tens to hundreds of μm | High signal integrity   |

| Silicon Interposers | Tens of μm             | Enhanced bandwidth      |

| Backside Power      | Sub-5nm                | Improved power delivery |

Table 12. Gate Length Scaling Challenges at 3nm

The fabrication process encompasses five distinct steps, utilizing the Bosch method for reactive ion etching. This approach alternates between etching using SF6 gas and passivation with C4F8 in multiple cycles, ensuring precise via formation.

#### 5.3 Die-to-Die Connections

Die-to-die interfaces represent a fundamental shift from traditional chip-to-chip connections, offering exceptional power efficiency alongside bandwidth improvements. These interfaces typically comprise PHY and controller blocks, facilitating seamless connectivity between internal interconnect fabrics.

Recent advancements in die-to-die technology demonstrate remarkable capabilities as in Fig. 7 [1, 2].

Figure 7. Packaging configuration [52]

- Power Efficiency: Multi-die implementations achieve power consumption levels comparable to monolithic solutions.

- 2. **Bandwidth Efficiency:** Advanced server applications support data transfers up to 112 Gbps per

- Latency Management: Simplified protocols connect directly to chip interconnect fabric, minimizing delays.

The interface between dies addresses critical requirements through innovative solutions. Short-reach, low-loss channels eliminate significant discontinuities, alongside implementing sophisticated error detection mechanisms. These interfaces incorporate forward error correction (FEC) and retry protocols, ensuring robust communication between dies.

Recent developments showcase successful implementation of Face-to-Face 3D SoIC technology, integrating 9 dies and 6 HBM stacks within a single package. This achievement underscores the maturity of 3D integration techniques in contemporary semiconductor manufacturing. Accordingly, the industry continues advancing standardization efforts, primarily focusing on inter-chiplet protocols and physical descriptions [53].

# 6. Manufacturing Process Advancements

Extreme ultraviolet (EUV) lithography stands as the cornerstone of advanced semiconductor manufacturing, enabling precise fabrication of 2nm chips through sophisticated process control. The

integration of cutting-edge manufacturing techniques alongside rigorous quality assurance protocols marks a new chapter in semiconductor production.

# 6.1 EUV Lithography Implementation

The semiconductor industry has embraced EUV lithography as the primary enabler for 2nm chip production. ASML's Twinscan NXE:3800E scanner demonstrates remarkable capabilities, processing up to 220 wafers per hour at a 30mj/cm² dose. This advanced system facilitates unprecedented precision in pattern transfer, essential for achieving the intricate features of 2nm technology as in Table 13:

| <b>EUV System Specifications</b> | Performance Metrics |

|----------------------------------|---------------------|

| Wafer Processing Speed           | 220 wafers/hour     |

| Exposure Dose                    | 30mj/cm²            |

| Monthly Wafer Capacity           | 17,000-20,000       |

| EUV Layer Count                  | 20 layers           |

Table 13. Gate Length Scaling Challenges at 3nm

The implementation of EUV technology requires substantial infrastructure investment. Rapidus, for instance, plans to deploy 10 EUV lithography machines across its production sites. This strategic deployment aims to achieve optimal production capacity, considering the complex requirements of 2nm chip fabrication.

Process stability demands constant vigilance alongside sophisticated fine-tuning mechanisms. The manufacturing process incorporates intensive research efforts targeting multiple aspects as in Table 14:

| Research Focus Areas      | Technical Objectives        |

|---------------------------|-----------------------------|

| Novel Resist Materials    | Enhanced pattern resolution |

| Light Source Stability    | Improved throughput         |

| Mask Writing Precision    | Reduced defect rates        |

| Al-driven Process Control | Optimized yield management  |

Table 14. Gate Length Scaling Challenges at 3nm

## 6.2 Quality Control Systems

Quality assurance in 2nm chip production encompasses comprehensive metrology systems alongside sophisticated particle detection mechanisms. The semiconductor industry demands extreme precision, where even seemingly negligible imperfections can lead to significant consequences.

Advanced particle detection systems now enable measurements down to 2nm, ensuring unprecedented control over process gas purity. These systems operate based on three key specifications as in Table 15:

Metrology plays a vital role in identifying plus correcting defects that might reduce yield. Through accurate measurements of wafer plus device characteristics at various production stages, metrology tools enable engineers to detect issues early, before they manifest in fully formed devices.

The quality control framework incorporates sophisticated feedback loops essential for continuous process optimization. Higher sampling flow rates prove valuable in process gas monitoring, pri-

| Quality Control Parameter | Implementation Details       |

|---------------------------|------------------------------|

| Particle Size Detection   | Down to 2nm resolution       |

| False Count Rate          | Minimized for accuracy       |

| Flow Rate Optimization    | Enhanced sampling efficiency |

Table 15. Gate Length Scaling Challenges at 3nm

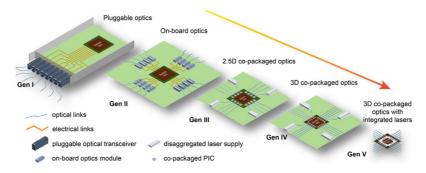

marily because of the extreme cleanliness requirements. Given the scarcity of particles available for testing, statistical considerations become crucial as in Fig. 8.

Figure 8. Co-packaging technologies [54]

Data accuracy emerges as foundational to decision-making processes. A low zero-count rate in measurement instruments signifies high data accuracy, ultimately minimizing false alarms plus enhancing manufacturing efficiency. This precision-driven approach ensures that each step in the production process aligns with exacting standards, maintaining consistently high yields even as designs become increasingly complex.

The integration of AI-driven metrology tools analyzes process variability in real-time, enabling dynamic adjustments to scanner parameters. These systems monitor over 1,000 equipment plus process parameters, ensuring quality outcomes through sophisticated characterization plus monitoring protocols. Alongside traditional inspection methods, advanced imaging techniques facilitate comprehensive defect analysis, ensuring that each chip meets stringent quality requirements.

#### 7. Performance Benchmarks

Benchmark data from TSMC's 2nm process reveals substantial improvements across multiple performance metrics, setting new standards for semiconductor manufacturing. Initial testing demonstrates remarkable advancements in processing capabilities, power consumption, plus transistor density.

#### 7.1 Processing Speed Metrics

The 2nm process technology showcases exceptional speed improvements through its innovative nanosheet transistor design. Performance testing indicates a 15% increase in processing speed at identical power levels compared to the previous 3nm node. This enhancement stems primarily from superior gate control plus reduced parasitic capacitance as in Table 16:

The ARM Cortex-A715 core, manufactured using 2nm technology with high-performance standard library, demonstrates exceptional capabilities. Testing reveals a 16.4% speed increase at constant

Performance ParameterImprovement vs 3nmProcessing Speed15% fasterGate ControlEnhanced nanosheet designARM Cortex-A715 Speed16.4% faster at same power

Table 16. Gate Length Scaling Challenges at 3nm

power levels versus the same core produced on 3nm process. These results underscore the substantial performance gains achievable through 2nm fabrication.

## 7.2 Energy Efficiency Data

Power consumption metrics highlight remarkable improvements in energy efficiency. Testing shows a 30% reduction in power usage while maintaining equivalent performance levels. This advancement proves especially crucial for mobile devices plus high-performance computing applications as in Table 17:

| Power Efficiency Metric | Result                     |

|-------------------------|----------------------------|

| Power Reduction         | 30% at iso-performance     |

| ARM Core Power Savings  | 37.2% at same speed        |

| Voltage Requirements    | 0.8V for optimal operation |

Table 17. Gate Length Scaling Challenges at 3nm

The ARM Cortex-A715 core exhibits exceptional power characteristics, achieving 37.2% power savings at identical operating speeds. Operating at 0.8V, the core simultaneously delivers 10% higher speed alongside 20% reduced power consumption. These improvements stem from enhanced electrostatic control offered by gate-all-around transistor design.

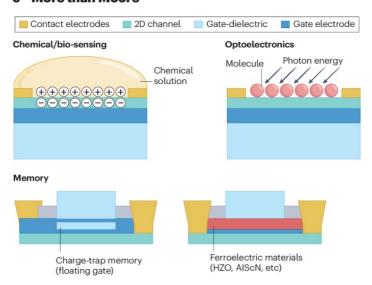

#### 7.3 Density Improvements

Transistor density advancements mark a significant milestone in semiconductor evolution. The 2nm process achieves a 1.15 times increase in transistor density compared to its predecessor. This enhancement enables manufacturers to pack more computational power into smaller chip areas as in Fig. 9.

SRAM scaling demonstrates unprecedented progress, with HD SRAM bit cell size shrinking to approximately 0.0175  $\mu m^2$ . This reduction enables SRAM density of 38 Mb/mm², marking substantial improvement from previous nodes. Gate-all-around nanosheet transistors facilitate this advancement through superior electrostatic control plus precise threshold voltage tuning.

Recent testing reveals encouraging yield rates, essential for commercial viability. SRAM yield rates have shown steady improvement as in Table 18:

**Table 18.** Gate Length Scaling Challenges at 3nm

| Time Period | 256 Mb SRAM Yield |

|-------------|-------------------|

| April 2023  | 35%               |

| March 2024  | 70%               |

## a 3D integration of 2D electronics

## b 'More Moore'

## c 'More than Moore'

Figure 9. Schematic of 3D integration of 2D electronics [55]

Device performance continues improving steadily, achieving higher frequencies without increasing power consumption. The implementation of N2 NanoFlex technology enables manufacturers to compress more logic cells into smaller areas, optimizing surface utilization. These density im-

provements, alongside enhanced yield rates, establish 2nm technology as a viable solution for next-generation semiconductor manufacturing.

# 8. Real-world Applications

The practical applications of 2nm chip technology span across multiple domains, fundamentally altering how we process data plus execute complex computations. These advancements unlock possibilities in artificial intelligence, scientific research, plus mobile computing, setting fresh benchmarks for device performance.

## 8.1 AI/ML Processing Units

The integration of 2nm technology into AI processing units marks a substantial leap forward in computational capabilities. Recent testing demonstrates that 2nm chips achieve 45% higher performance compared to 7nm chips while maintaining identical power consumption levels. This enhancement primarily benefits AI workloads requiring immense computational resources as in Table 19:

| AI Application       | Performance Enhancement |

|----------------------|-------------------------|

| Model Training       | 45% faster processing   |

| Real-time Inference  | 75% power reduction     |

| On-device Processing | 4x battery efficiency   |

Table 19. Gate Length Scaling Challenges at 3nm

The implementation of 2nm technology enables sophisticated on-device AI operations, from enhanced photo editing to real-time language translation. Through advanced voltage distribution systems, these chips maintain optimal performance levels across varying workloads.

#### 8.2 High-Performance Computing

High-performance computing applications showcase the full potential of 2nm technology through enhanced processing capabilities plus improved energy management. The architecture demonstrates remarkable versatility across diverse computing scenarios as in Table 20:

| Computing Metric   | Performance Impact |

|--------------------|--------------------|

| Processing Speed   | 25% increase       |

| Power Efficiency   | 20-30% reduction   |

| Transistor Density | 20% improvement    |

Table 20. Gate Length Scaling Challenges at 3nm

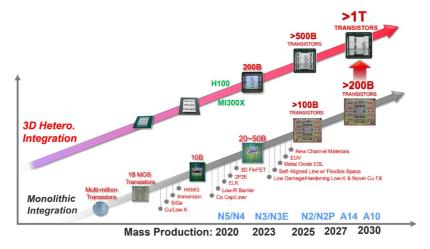

TSMC's N2 process technology, scheduled for production in 2025, introduces significant improvements in computing performance. The process offers 10-15% higher performance at equivalent power consumption levels, alternatively delivering 20-30% lower power usage while maintaining consistent performance as in Fig. 10.

The implementation of backside power delivery networks alongside advanced voltage distribution systems enables stable operation under intensive computational loads. This innovation reduces platform voltage droop by 30% plus increases frequency performance by 6%.

Figure 10. Moore's law [56]

# 8.3 Mobile Device Integration

Mobile devices represent a primary beneficiary of 2nm chip technology, experiencing substantial improvements in battery life plus processing capabilities. Initial testing indicates that smartphones equipped with 2nm processors could quadruple battery life compared to devices using 7nm technology as in Table 21:

| Mobile Feature       | Enhancement        |

|----------------------|--------------------|

| Battery Life         | 4x improvement     |

| App Launch Speed     | 15% faster         |

| Graphics Processing  | Enhanced rendering |

| Network Connectivity | 6G ready           |

Table 21. Gate Length Scaling Challenges at 3nm

The practical implications prove remarkable - mobile devices utilizing 2nm chips require charging only once every four days under average usage conditions. These improvements stem from sophisticated power management systems plus enhanced transistor efficiency as in Table 22:

Beyond basic performance metrics, 2nm technology enables advanced features in mobile devices. The reduced chip size creates opportunities for slimmer device profiles plus enhanced cooling systems. Additionally, the technology supports future connectivity standards, ensuring devices remain capable of handling upcoming 6G networks plus advanced communication protocols.

Medical applications benefit similarly from these advancements, with 2nm technology enabling sophisticated wearable health monitors capable of real-time data analysis while consuming minimal power. The automotive sector likewise sees substantial gains, as 2nm chips prove instrumental in advancing self-driving technologies plus improving safety systems as in Fig. 11.

| Mobile Feature       | Enhancement        |

|----------------------|--------------------|

| Battery Life         | 4x improvement     |

| App Launch Speed     | 15% faster         |

| Graphics Processing  | Enhanced rendering |

| Network Connectivity | 6G ready           |

Table 22. Gate Length Scaling Challenges at 3nm

Figure 11. TSMC 1nm prediction [57]

The implementation of these chips across various sectors demonstrates their versatility. Data centers, for instance, could significantly reduce their carbon footprint by transitioning to 2nm-based processors. Similarly, laptop computers experience notable improvements in processing speed, language translation capabilities, plus internet access performance.

The remarkable journey through 2nm chip technology demonstrates unprecedented advancements across semiconductor manufacturing. Performance metrics showcase substantial improvements that reshape computing capabilities as in Table 23:

| Performance Metric | Improvement         |

|--------------------|---------------------|

| Processing Speed   | 15% faster than 3nm |

| Power Efficiency   | 30% reduction       |

| Transistor Density | 1.15x increase      |

| SRAM Density       | 38 Mb/mm²           |

Table 23. Gate Length Scaling Challenges at 3nm

The industry roadmap points toward rapid adoption across various sectors as in Table 24:

# 9. Conclusion

These achievements stem from multiple breakthrough innovations, particularly the implementation of gate-all-around transistors and backside power delivery networks. The sophisticated thermal

| Timeline | Implementation Milestone       |

|----------|--------------------------------|

| 2024     | Design pathfinding PDK release |

| 2025     | TSMC mass production start     |

| 2026     | Mobile device integration      |

| 2027     | Data center deployment         |

Table 24. Gate Length Scaling Challenges at 3nm

management systems, coupled with advanced materials science developments, enable reliable operation under demanding conditions. The successful integration of 3D stacking techniques alongside EUV lithography advancements establishes a solid foundation for future semiconductor evolution. Power delivery innovations, particularly the backside power delivery network, address critical challenges in voltage distribution and heat management. The practical applications span diverse fields, from artificial intelligence acceleration to mobile computing. Medical devices, automotive systems, and data centers stand ready to benefit from enhanced processing capabilities and reduced power consumption. These improvements promise transformative changes in how we approach computing challenges across industries. The semiconductor industry stands at a pivotal moment where theoretical limits meet practical innovation. The 2nm process node represents more than technological advancement - it symbolizes our ability to push boundaries while maintaining reliability and efficiency. Through continued research and development, we expect to witness even more remarkable achievements in semiconductor manufacturing.

#### References

- [1] Kumar Vishal. "Bandgap Engineering of 2D Materials and its Electric and Optical Properties". In: (2023).

- [2] Yushin Kim, Byoung Jun Park, Moohyuk Kim, Young-Ho Jin, Nu-Ri Park, and Myung-Ki Kim. "Light engineering in nanometer space". In: *Advanced Materials* 32.51 (2020), p. 2003051.

- [3] Guru Pada Chattopadhyay. Technologies in the Era of Singularity. Notion Press, 2018.

- [4] Steven Herschbein, Shida Tan, Richard Livengood, and Michael Wong. "Focused Ion Beam (FIB) for Chip Circuit Edit and Fault Isolation". In: *ISTFA 2021*. ASM International. 2021, h1–h113.

- [5] Mads Boye, Ole Holm Nielsen, Pietro Antonio Bortolozzo, Niels Carl Hansen, Hans Henrik Happe, Erik Madsen, and Jannick Visling. "DeiC Super Computing 2019 Report: Fact Finding Tour at Super Computing 19, November-Denver, Colorado". In: (2020).

- [6] Marc J Madou. Fundamentals of microfabrication: the science of miniaturization. CRC press, 2018.

- [7] Sarah Afiq, Maryam Fikri, Rahman Ethan, and Amsyar Isfahann. "Acknowledging the Role of Buck Converter in DC-DC Conversion". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 3.1 (2022), pp. 287–301.

- [8] Georges Adam, Amine Benouhiba, Kanty Rabenorosoa, Cédric Clévy, and David J Cappelleri. "4D printing: Enabling technology for microrobotics applications". In: *Advanced Intelligent Systems* 3.5 (2021), p. 2000216.

- [9] John H Lau. "Recent advances and trends in Cu–Cu hybrid bonding". In: *IEEE Transactions on Components, Packaging and Manufacturing Technology* 13.3 (2023), pp. 399–425.

- [10] Er-Ping Li, Hanzhi Ma, Manareldeen Ahmed, Tuomin Tao, Zheming Gu, Mufeng Chen, Quankun Chen, Da Li, and Wenchao Chen. "An electromagnetic perspective of artificial intelligence neuromorphic chips". In: *Electromagnetic Science* 1.3 (2023), pp. 1–18.

- [11] Corey Richard. "Understanding Semiconductors". In: ().

- [12] Henry H Radamson, Yuanhao Miao, Ziwei Zhou, Zhenhua Wu, Zhenzhen Kong, Jianfeng Gao, Hong Yang, Yuhui Ren, Yongkui Zhang, Jiangliu Shi, et al. "CMOS scaling for the 5 nm node and beyond: Device, process and technology". In: *Nanomaterials* 14.10 (2024), p. 837.

- [13] Fernanda Hernández, Leonardo Sánchez, Gabriela González, and Andrés Ramírez. "Revolutionizing CMOS VLSI with Innovative Memory Design Techniques". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 3.2 (2022), pp. 366–379.

- [14] Kyle Johnson Dorsey. Atomic layer deposition for mechanical, magnetic, and robotic systems. Cornell University, 2020.

- [15] Matthew Delaney. "The integration of chalcogenide materials with nanophotonic circuits for recongurable control of light". PhD thesis. University of Southampton, 2020.

- [16] Ammar Nayfeh and Nazek El-Atab. *Nanomaterials-Based Charge Trapping Memory Devices*. Elsevier, 2020.

- [17] Sehtab Hossain. Function Implementation in a Multi-Gate Junctionless FET Structure. University of Missouri-Kansas City, 2023.

- [18] DI MOSTAGANEM. "Study and Simulation of a Nanoscale Structure of a Multi-gate MOS Transistor". In: ().

- [19] NOUR EL Boukortt. "Study and Simulation of a Nanoscale Structure of a Multi-gate MOS Transistor". In: (2017).

- [20] Kyle Chang. "Carrier Card for Nvidia Jetson AGX Xavier". In: (2022).

- [21] Ed Sperling. *The Rising Price Of Power In Chips semiengineering.com.* https://semiengineering.com/the-rising-price-of-power-in-chips/. [Accessed 11-10-2024].

- [22] Daan Swinkels. "Spectral Shaping for Next-Generation Overlay Metrology". In: ().

- [23] Usman Bature Isyaku, Mohd Haris Bin Md Khir, I Md Nawi, MA Zakariya, and Furqan Zahoor. "ZnO based resistive random access memory device: a prospective multifunctional next-generation memory". In: *IEEE Access* 9 (2021), pp. 105012–105047.

- [24] Doried Ghader. "The 2021 Magnonics Roadmap". In: ().

- [25] Shira Rubin, Daniel Mizrachi, Noam Friedman, Hila Edri, and Tamar Golan. "The World of Advanced Thin Films: Design, Fabrication, and Applications". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 4.1 (2023), pp. 393–406.

- [26] Jason Michael Haber. "Microfluidic PCR with plasmonic imaging for rapid multiplexed characterization of DNA from microbial pathogens". PhD thesis. 2016.

- [27] Jonathan David Coburn. *Erosion Characterization of Advanced Plasma Facing Materials (PFMs)* for Magnetic Fusion Reactors. North Carolina State University, 2018.

- [28] Paul Timmers. *Digital industrial policy for Europe*. Vol. 13. Centre on Regulation in Europe, 2022.

- [29] Henry H Radamson, Yuanhao Miao, Ziwei Zhou, Zhenhua Wu, Zhenzhen Kong, Jianfeng Gao, Hong Yang, Yuhui Ren, Yongkui Zhang, Jiangliu Shi, et al. "CMOS scaling for the 5 nm node and beyond: Device, process and technology". In: *Nanomaterials* 14.10 (2024), p. 837.

- [30] Sean Tan, Wei Lee, Chloe Wong, and Yi Jia Chua. "Exploring the Potential and Advancements of Hydrogen Fuel Cells: Outcomes and Applications". In: *Fusion of Multidisciplinary Research, An International Journal (FMR)* 4.1 (2023), pp. 407–419.

- [31] Amit Sangwan. "Connecting Optical Communications with Bio-Sensing and Bio-Actuation". PhD thesis. Northeastern University, 2022.

- [32] Zheng Yong. Optimized PN Junctions and Three-dimensional Integration for Carrier-depletion Silicon Optical Modulators. University of Toronto (Canada), 2019.

- [33] Paweł Bajurko, Jakub Sobolewski, Yevhen Yashchyshyn, Pavlo Sai, Sergey L Rumyantsev, Teodor Narytnyk, and Grzegorz Cywiński. "AlGaN/GaN Distributed Schottky Barrier Single-Pole Single-Throw Millimeter-Wave Switches". In: *IEEE Access* 11 (2023), pp. 125909–125917.

- [34] Brett Thomas and Annika Lohstroh. "Charge Loss Characterisation and Correction in Compound Semiconductor Detectors for Spectroscopic X-Ray Imaging". In: (2018).

- [35] Anastasia Klymenko, Snizhana Shevchenko, Rostislav Marchenko, and Dmitriy Tkachenko. "Electrode Batteries: Organic Material's influence on Lithium-Ion Battery Performance". In: *Fusion of Multidisciplinary Research, An International Journal (FMR)* 4.2 (2023), pp. 458–470.

- [36] Cheng Chih Hsieh. "Cerium oxide based resistive random access memory devices". PhD thesis. 2017.

- [37] Anthony Rizzo. *Highly Parallel Silicon Photonic Links with Integrated Kerr Frequency Combs.* Columbia University, 2022.

- [38] Renfa Liu, Yunxue Xu, Nisi Zhang, Shuai Qu, Wenlong Zeng, Rui Li, and Zhifei Dai. "Nanotechnology for enhancing medical imaging". In: *Nanomedicine*. Springer, 2023, pp. 99–156.

- [39] Mark LaPedus. *Breaking The 2nm Barrier semiengineering.com.* https://semiengineering.com/breaking-the-2nm-barrier/. [Accessed 11-10-2024].

- [40] Haziq Ahmad, Syafiq Khan, Zulhasif Tan, and Rayzal Hamid. "Invariants in Birational Mapping: An In-Depth and Comprehensive Guide to Their Properties, Applications, and Mathematical Significance". In: *Fusion of Multidisciplinary Research, An International Journal (FMR)* 5.1 (2024), pp. 529–540.

- [41] Robert Marvel. *Physics and Processing of Vanadium Dioxide for Optical Devices*. Vanderbilt University, 2016.

- [42] Colin Alexander Fernandes. "Electrospun PEDOT: PSS Electrolytic Capacitors Electrodes for Microelectronic Energy Storage". PhD thesis. Carleton University, 2019.

- [43] Siddhartha Roy and Tapas K Kundu. Chemical biology of the genome. Academic Press, 2021.

- [44] Kelly Damalou. *The Computational Electromagnetics Simulation Challenge Of 3D-IC semiengineering.com.* https://semiengineering.com/the-computational-electromagnetics-simulation-challenge-of-3d-ic/. [Accessed 11-10-2024].

- [45] Greyson John Hodges. *Textiles and composite testing in extreme environments*. North Carolina State University, 2023.

- [46] Razvan Baba. "Resonant tunnelling diodes for THz communications". PhD thesis. University of Glasgow, 2018.

- [47] Jakob Alexander Genser. "Synthesis and strain engineering of 2D dirac materials". PhD thesis. Technische Universität Wien, 2021.

- [48] W Yu, T Yu, and GEW Bauer. "Indirect interactions between magnets". In: *Journal of Physics: Condensed Matter* 33.41 (2021), pp. 55–56.

- [49] Daniel Yimam. "Phase-change thin films growth and functionality: towards phase-change memory and reconfigurable nanophotonics". In: (2023).

- [50] Robert Fennell. "The Development of Wide-Field Bio-Imaging for Point of Care Diagnostic Assays in Resource Constrained Settings". PhD thesis. Florida Atlantic University, 2021.

- [51] Ang-Sheng Chou, Ching-Hao Hsu, Yu-Tung Lin, Goutham Arutchelvan, Edward Chen, Terry YT Hung, Chen-Feng Hsu, Sui-An Chou, Tsung-En Lee, Oreste Madia, et al. "Status and Performance of Integration Modules Toward Scaled CMOS with Transition Metal Dichalcogenide Channel". In: 2023 International Electron Devices Meeting (IEDM). IEEE. 2023, pp. 1–4.

- [52] Gregory Haley. Closing The Test And Metrology Gap In 3D-IC Packages semiengineering.com. https://semiengineering.com/closing-the-test-and-metrology-gap-in-3d-ic-packages/. [Accessed 11-10-2024].

- [53] Liam Connor, Rebecca Kelly, Saoirse Murphy, Eoghan McCarthy, and Edward Murray. "Analysis of AutoML Tools in the World of Automated Deep Learning". In: Fusion of Multidisciplinary Research, An International Journal (FMR) 5.1 (2024), pp. 541–555.

- [54] Morteza Sasani Ghamsari. "Chip-scale quantum emitters". In: *Quantum Reports* 3.4 (2021), pp. 615–642.

- [55] Darsith Jayachandran, Najam U Sakib, and Saptarshi Das. "3D integration of 2D electronics". In: *Nature Reviews Electrical Engineering* 1.5 (2024), pp. 300–316.

- [56] James McKenzie. *Moore's law: further progress will push hard on the boundaries of physics and economics Physics World physicsworld.com.* https://physicsworld.com/a/moores-law-further-progress-will-push-hard-on-the-boundaries-of-physics-and-economics/. [Accessed 11-10-2024].

- [57] Muhammad Zuhair. *TSMC Starts Preparing For 1nm Production, Plans For a Cutting-Edge Facility In Taiwan wccftech.com.* https://wccftech.com/tsmc-starts-preparing-1nm-production-plans-cutting-edge-facility-taiwan/. [Accessed 11-10-2024].